Laporan Akhir 1 Modul 2

kondisi 1

Saat B0=0, B1=1, B2=don't care, B3=don't care, B4=don't care, B5=don't care, dan B6=don't care, maka dihasilkan output yang sama pada J-K Flip Flop dan D Flip Flop dimana Q=0 dan Q'=1.

kondisi 2

Saat B0=1, B1=0, B2=don't care, B3=don't care, B4=don't care, B5=don't care, dan B6=don't care, maka dihasilkan output pada J-K Flip Flop 1 dan pada D Flip Flop juga 1. Ini dikarenakan pada rangkaian ini dia aktif low, dan diberi inputan berupa 0, maka akan membuat rangkaiannnya mengeluarkan output sebesar 1

kondisi 3

Saat B0=0, B1=0, B2=don't care, B3=don't care, B4=don't care, B5=don't care, dan B6=don't care, maka dihasilkan output yang sama pada J-K Flip Flop dan D Flip Flop dimana Q=1 dan Q'=1. Kondisi ini dinamakan kondisi terlarang, karena Q dan Q' memiliki nilai yang sama yaitu 1. Seharusnya untuk nilai Q dan Q' itu berlawnana satu sama lain, tetapi pada kali ini, dia memiliki nilai yang sama(kondisi terlarang)

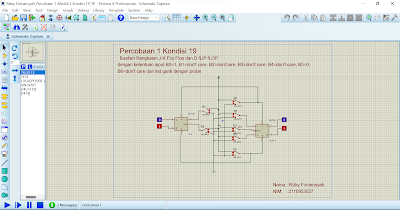

kondisi 4

Saat B0=1, B1=1, B2=0, B3=toggle, B4=0, B5=0, dan B6=⇨, maka dihasilkan output pada J-K Flip Flop adalah Q=1 dan Q'=0, sedangkan pada D Flip Flop nilai yang diperoleh adalah Q=0 dan Q'=1.

kondisi 5

Saat B0=1, B1=1, B2=0, B3=toggle, B4=1, B5=1, dan B6=⇨, maka dihasilkan output pada J-K Flip Flop adalah Q=0 dan Q'=1, sedangkan pada D Flip Flop nilai yang diperoleh adalah Q=0 dan Q'=1.

kondisi 6

Saat B0=1, B1=1, B2=1, B3=toggle, B4=0, B5=don't care, dan B6=0, maka dihasilkan output pada J-K Flip Flop adalah Q=1 dan Q'=0, sedangkan pada D Flip Flop nilai yang diperoleh adalah Q=0 dan Q'=1

kondisi 7

Saat B0=1, B1=1, B2=1, B3=toggle, B4=1, B5 dan B6 diputus, maka dihasilkan output adalah toggle, dimana ia berlawanan dengan ouput sebelumnya. Dimana sebelumnya outputnya adalah Q=1 dan Q'=0. Tetapi setelah dia bersifat toggle, maka untuk outputnya yang dihasilka adalah Q=0 dan Q'=1.

6. Analisa[Kembali]

pengaruh dari pin R dan S pada masing-masing flip-flop:

JK (J-K) Flip-Flop:

- Ketika J = 0 dan K = 0, flip-flop mempertahankan keadaan saat ini (keadaan terkunci).

- Ketika J = 0 dan K = 1, flip-flop direset ke keadaan nol.

- Ketika J = 1 dan K = 0, flip-flop diatur ke keadaan satu.

- Ketika J = 1 dan K = 1, flip-flop akan bergantung pada keadaan sebelumnya. Jika sebelumnya adalah 0, flip-flop akan diatur menjadi 1, dan jika sebelumnya adalah 1, flip-flop akan direset menjadi 0.

- R dan S dalam JK flip-flop adalah pemetaan langsung dari J dan K:

- Ketika R = 0 dan S = 0, flip-flop mempertahankan keadaan saat ini.

- Ketika R = 0 dan S = 1, flip-flop direset ke keadaan nol.

- Ketika R = 1 dan S = 0, flip-flop diatur ke keadaan satu.

- Ketika R = 1 dan S = 1, flip-flop akan bergantung pada keadaan sebelumnya seperti pada masukan J-K.

D Flip-Flop:

- Ketika D = 0, flip-flop direset ke keadaan nol.

- Ketika D = 1, flip-flop diatur ke keadaan satu.

- R dan S dalam D flip-flop dapat dilihat sebagai:

- Ketika R = 0 dan S = 0, flip-flop mempertahankan keadaan saat ini.

- Ketika R = 0 dan S = 1, flip-flop direset ke keadaan nol.

- Ketika R = 1 dan S = 0, flip-flop diatur ke keadaan satu.

- Ketika R = 1 dan S = 1, perilaku flip-flop tidak ditentukan dan dapat menyebabkan keadaan tak terduga (tidak disarankan).

Tidak ada komentar:

Posting Komentar